Clock

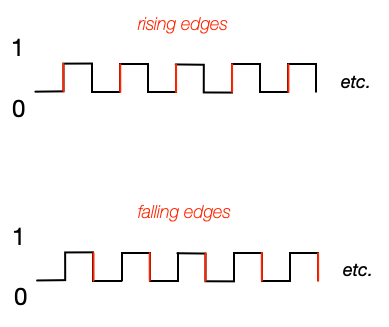

Many sequential and other circuits rely on a clock signal to control when data is stored or updated. A clock is a repeating square wave that alternates between 0 (low) and 1 (high) at a fixed frequency.

In systems or subsystems that are synchronized to a clock, you can think of the clock as a metronome, providing a “rhythm” for the system. Instead of changing outputs immediately when inputs change, flip-flops and registers wait for a clock edge to update data. Circuits can be designed to respond to the rising edge of a clock pulse (transition from 0 to 1), or the falling edge of the pulse (from 1 to 0).

Synchronization ensures that all parts of a system are updated together, avoiding race conditions and unpredictable behavior.

For example:

A D flip-flop propagates its input D to output Q only at the rising edge of the clock.

A register updates all of its stored bits simultaneously at each clock tick.

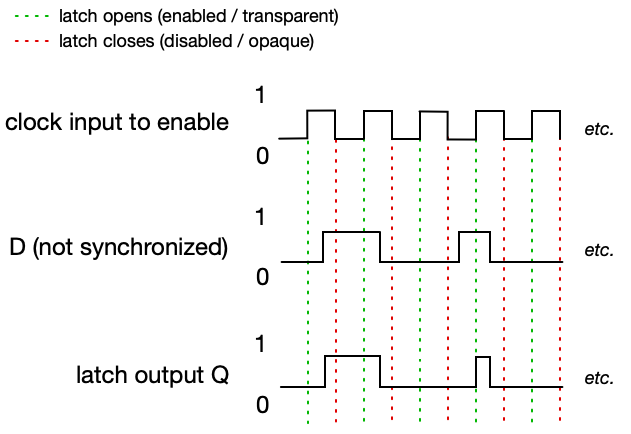

Here’s an example of a D latch in which the clock input is sent to the latch’s ENABLE line. Notice that the state of the latch (indicated by Q) changes at any time while the ENABLE signal is high.

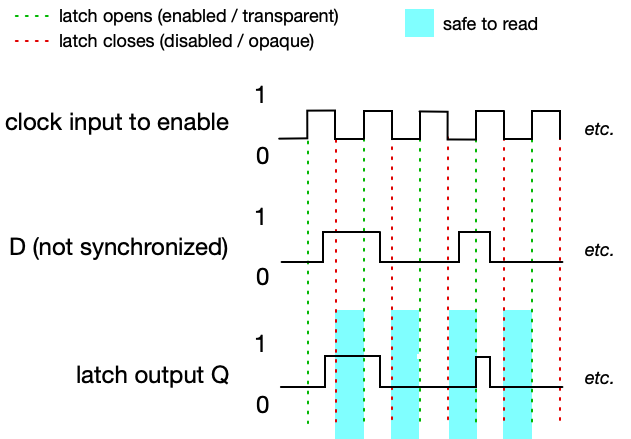

While a latch is enabled for some interval, its output can change if D changes at any time during that interval. Accordingly, it’s only safe to read from a “synchronized” D latch when it’s disabled—because the value can change if it’s enabled! Put another way, we cannot treat the value of a latch as stable when the latch is enabled (open, transparent).

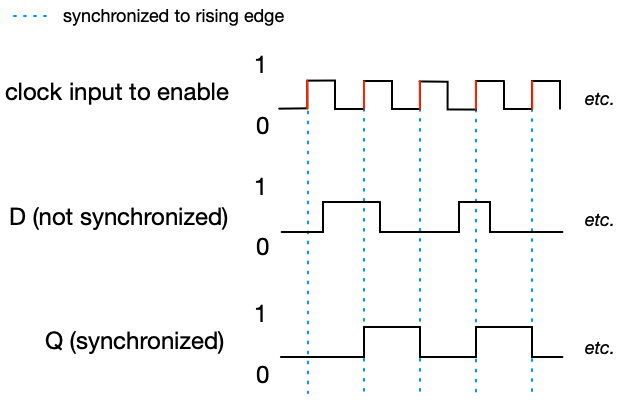

This is why we have flip-flops. Flip-flops use two latches, one of which receives the inverted clock signal. By this design, a flip-flop is synchronized to the rising edge of the clock pulse. Instead of changing state based on the level of the ENABLE input (as with a single latch), a flip-flop only changes state on a rising pulse. The flip-flop’s logic ensures that one latch captures data while the next stage is locked out, preventing races and undefined intermediate values. You may think of this as sampling from D on rising pulses. Even if the input D is not synchronized (rising and falling edges of the D signal don’t coincide with rising and falling edges of the clock), the output of the flip-flop is synchronized.

Thus, clocked sequential circuits like flip-flops and registers update only in step with the clock, ensuring that data moves through the system in a predictable, orderly fashion.

Clocks are used to synchronize circuits and to orchestrate interaction between circuits. Clock frequency (measured in Hertz, cycles per second) sets the pace of computation and interactions. A 2 GHz clock ticks two billion times per second, meaning the CPU can potentially perform billions of synchronized updates each second.

© 2025 Clayton Cafiero.

No generative AI was used in writing this material. This was written the old-fashioned way.